ChatGPT强势加入芯片设计,不用学专业硬件描述语言了,说人话就行

和 ChatGPT 聊聊天,就可解决 CPU 开发过程中的一大难题?

纽约州立大学研究人员完成了一件看似不可能的事情:

无需专业的硬件描述语言,仅靠说人话就能设计芯片!

在 ChatGPT 的帮助下,他们不仅设计出 CPU 上的一个组件,甚至还通过了有效性验证环节。

这个组件主要负责创造出一种基于八位累加器的微处理器架构的逻辑。而累加器本质上是寄存器,是专门存放算术或逻辑运算的一个操作数和存储运算结果的。而这是 CPU 运作中不可或缺的一部分。

所以,还有什么是大语言模型不能做的?

有网友表示:

芯片设计的部分流程实现自动化无疑是个好消息。

也有网友表现出对在芯片设计中使用 AI 编写 HDL 的担忧:

ChatGPT 对芯片设计干了啥?

通常,设计和制造芯片的过程中会经历几个阶段。

其中一个阶段是用硬件描述语言(例如 Verilog)描述芯片内不同部件的实际几何形状、密度和整体布局。

在此前,作为一个极其专业化和复杂的领域,HDL 编写一直是一项相对罕见且非常难以掌握的工作。

研究团队成员之一、也是研究助理教授的 Hammond Pearce 博士更是认为:

硬件描述语言的最大挑战就是没有多少人知道如何编写它们,很难成为这方面的专家。

这也就意味着,即使是最好的工程师也还是经常需要用这种语言做一些琐碎的事情。

而 ChatGPT 作为一种模式识别器,可以在各种类型的语言中转换自如,这就可以帮助工程师们跳过 HDL 阶段。

在这项研究中,研究人员分别使用 LLM 对八个具有代表性的硬件设计示例进行了研究。工程师与 LLM 之间实时来回交互,将纯英文文本逐步转化为 Verilog的等效代码。

其中一位硬件工程师与 LLMs 共同设计了一种新颖的基于八位累加器的微处理器体系结构。他们将这些基准测试和处理器发送到 Skywater 130 纳米 Shuttle 进行流片。

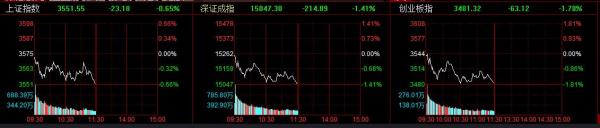

这个过程中,研究人员评估了 ChatGPT-4、ChatGPT-3.5、Bard、HuggingChat 四个不同 LLM 创建硬件设计的 Verilog 能力:

此外,研究人员还针对 8 位移位寄存器进行了基准测试。告诉大模型正在尝试为一个「测试名称」创建一个 Verilog 模型。然后提供规范说明,定义输入和输出端口以及其他所需的具体信息。最后询问他该如何编写一个满足这些规范的设计。

下面是不同大模型给出的设计方案:

如上图所示,虽然 ChatGPT 都能够满足规格要求并开始进行设计流程,但 Bard 和 HuggingChat 都未能满足规格要求的初始标准。

研究人员又基于 Bard 和 HuggingChat 的初始提示,让它们重新生成了五次回答,但两者还是都失败了。Bard 一直无法满足给定的设计规格要求,而 HuggingChat 的 Verilog 输出在模块定义之后就不符合语法规范。

鉴于 Bard 和 HuggingChat 在初始的挑战基准测试中表现不佳,研究人员决定后续完整测试仅对 ChatGPT-4 和 ChatGPT-3.5 进行。

与此同时,顺便让大模型进行了 Testbench的设计:

你能为这个设计编写一个 Verilog 测试台吗?测试台应该具备自检功能,并且能够与 iverilog 一起用于仿真和验证。如果测试用例失败,测试台应该能够提供足够的信息,以便找到并解决错误。

最终结果表明 ChatGPT-4 的表现较为出色。大多数基准测试都通过了,并且大部分只需要工具反馈即可。

与创建可运行设计相比,ChatGPT-4 在创建可运行的测试台上遇到了更多困难,往往还是需要人类的反馈意见。

而与 ChatGPT-4 相比,ChatGPT-3.5 的表现明显较差,大多数基准测试都失败了,而那些通过测试台的对话大多数也不符合规范。与 ChatGPT-4 相比,ChatGPT-3.5 每次对话和基准测试之间会出现各种各样的问题,在设计和测试台方面需要更频繁地进行修正。

ChatGPT 是芯片设计中的“力量倍增器”

随着大语言模型的继续发展,未来从构想到功能设计,LLM 或许都可以轻松实现。

研究人员认为:

尽管我们强调了模型的单步性能,但对于硬件应用来说,让它们以“共同设计师”的身份加入,可能会表现得更好。

当与经验丰富的工程师协同工作时,它们可以成为一种“力量倍增器”。工程师可以根据模型提供的“初版设计方案”,进行微调和快速迭代。

Hammond Pearce 博士说道:

这项研究成果是我们认为首次完全由人工智能生成的硬件描述语言转化为物理芯片的案例。

一些人工智能模型,比如 OpenAI 的 ChatGPT 和谷歌的 Bard,可以生成不同编程语言的软件代码,但它们在硬件设计领域的应用尚未被广泛研究。

而这项研究表明,人工智能在硬件制造方面也具有潜力,尤其是在对话式应用中,通过反复交流可以完善设计。

并且,这样一来 HDL 编写过程中人为引起的错误就会减少,从而可缩短设计时间和上市时间,也可允许更多创造性的设计。

不知一些 HDL 工程专家听到这里是否会略感紧张。

研究人员认为如果这个过程能够实现自动化,不仅可以加快现在的工作速度,还可以减轻人为瓶颈。

但是,完全依靠类似于 ChatGPT 这种大模型或者依赖电力运行的软件机器也存在一定的风险。用于芯片设计的 LLM 在训练阶段也存在难解的黑盒子等一系列问题。

对此,你有什么看法?

参考链接:

声明:本网转发此文章,旨在为读者提供更多信息资讯,所涉内容不构成投资、消费建议。文章事实如有疑问,请与有关方核实,文章观点非本网观点,仅供读者参考。

猜您喜欢